## **Product Specification For LCD Module**

Model NO.: CNKT0800-19306A2

**CUSTOMERITEM NO.:**

**REVISION: A**

□ APPROVAL FOR SPECIFICATIONS ONLY

**APPROVAL FOR SPECIFICATIONS AND SAMPLE**

CUSTOMER: APPROVED BY:

| CNK LCM R&D CENTER |            |             |  |  |  |

|--------------------|------------|-------------|--|--|--|

| APPROVED BY        | CHECKED BY | PREPARED BY |  |  |  |

| 432                | 最长的        |             |  |  |  |

| DIRECTOR           | MANAGER    | Engineer    |  |  |  |

#### 深圳市希恩凯电子有限公司

SHEN ZHEN CNK ELECTRONICS CO., LTD

地 址: 惠州市惠阳区西湖村铭仕工业园 2 栋 1-2 楼

电话: 0752-3556001 传真: 0752-3556004

http://www.szcnk.com

| ITEM            | CONTENTS                        |

|-----------------|---------------------------------|

| 1               | VERSION HISTORY                 |

| 2               | GENERAL INFORMATION             |

| 3               | BIOCK DIAGRAM                   |

| 4               | OPERATION SPECIFTCATIONS        |

| 5               | BACKLIGHT CHARACTERISTICS       |

| 6               | EXTERNAL DIMENSIONS             |

| 7               | INTERFACE SIGNALS               |

| 8               | SIGNAL TIMING CHARACTERISTICS   |

| 9               | ELECTRO-OPTICAL CHARACTERISTICS |

| 10              | RELIABILITY TEST                |

| 11              | QUALITY LEVEL                   |

| 12              | Package drawing                 |

| /17             |                                 |

| $/\gamma_{\pi}$ |                                 |

| 7//             |                                 |

|                 |                                 |

## **1**<sup>™</sup> VERSION HISTORY

| SAMPLE<br>VERSION | DATE        | DESCRIPTION                                                                        | REVISED BY |

|-------------------|-------------|------------------------------------------------------------------------------------|------------|

| A00               | 2018-12-27  | FIRST DEVELOPED                                                                    | Wenlu Liao |

| A01               | 2019-03-06  | Update PIN Definition (MIPI Signal) Description Section on Page 7 of Specification | Wenlu Liao |

|                   |             |                                                                                    |            |

|                   |             |                                                                                    |            |

|                   |             |                                                                                    |            |

|                   |             |                                                                                    |            |

|                   |             |                                                                                    |            |

|                   |             | X                                                                                  |            |

|                   | <b>4</b> XI |                                                                                    |            |

|                   |             |                                                                                    |            |

| 1                 | A A         |                                                                                    |            |

|                   | X ·         |                                                                                    |            |

| 7/                |             |                                                                                    |            |

|                   |             |                                                                                    |            |

|                   |             |                                                                                    |            |

|                   |             |                                                                                    |            |

## GENERAL INFORMATION

| Item                        | Contents                     | Unit                                                                               |

|-----------------------------|------------------------------|------------------------------------------------------------------------------------|

| LCD Size                    | 8.0                          | inch                                                                               |

| Driver element              | a-Si TFT active matrix       |                                                                                    |

| Viewing direction           | Normally black               |                                                                                    |

| Module size                 | 114.60(W)*184.10(H)*2.5(T)mm | mm                                                                                 |

| Panel Active Area           | 107.64(W)*172.22(H)          | mm                                                                                 |

| Number of Dots              | 800*RGB*1280                 | pixel                                                                              |

| Driver IC                   | ILI8881C                     |                                                                                    |

| Colors                      | 16.7M                        |                                                                                    |

| Surface Treatment           | Glare                        |                                                                                    |

| Interface                   | MIPI (4 Lane)                |                                                                                    |

| Brightness                  | 350cd/m²(typ)                |                                                                                    |

| NTSC                        | 55%(typ)                     |                                                                                    |

| Backlight power consumption | 1.37W(typ)                   | W                                                                                  |

| Panel power consumption     | TBD                          | W                                                                                  |

| Weight                      | TBD                          | g                                                                                  |

| Backlight Type              | LED                          | -                                                                                  |

| Operating Temperature       | -10℃50℃                      | $^{\circ}$                                                                         |

| Storage Temperature         | -20℃60℃                      | $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

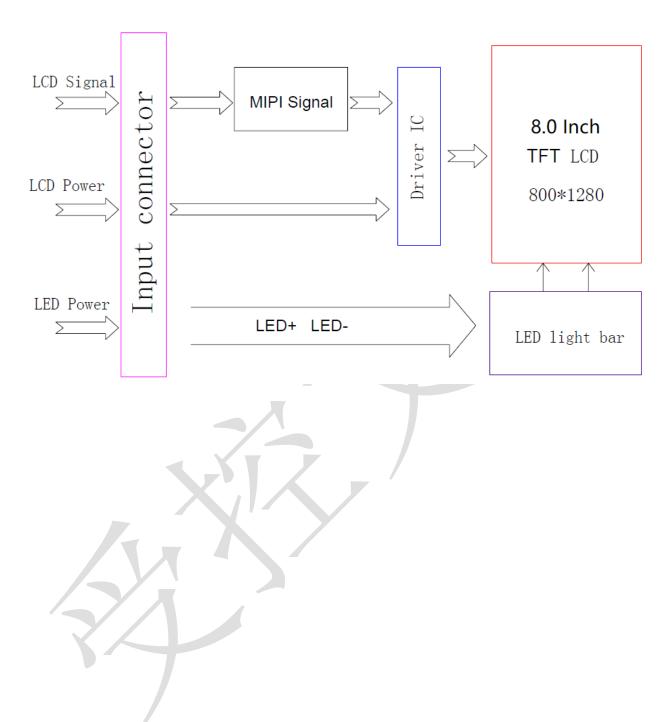

## **3™BIOCK DIAGRAM**

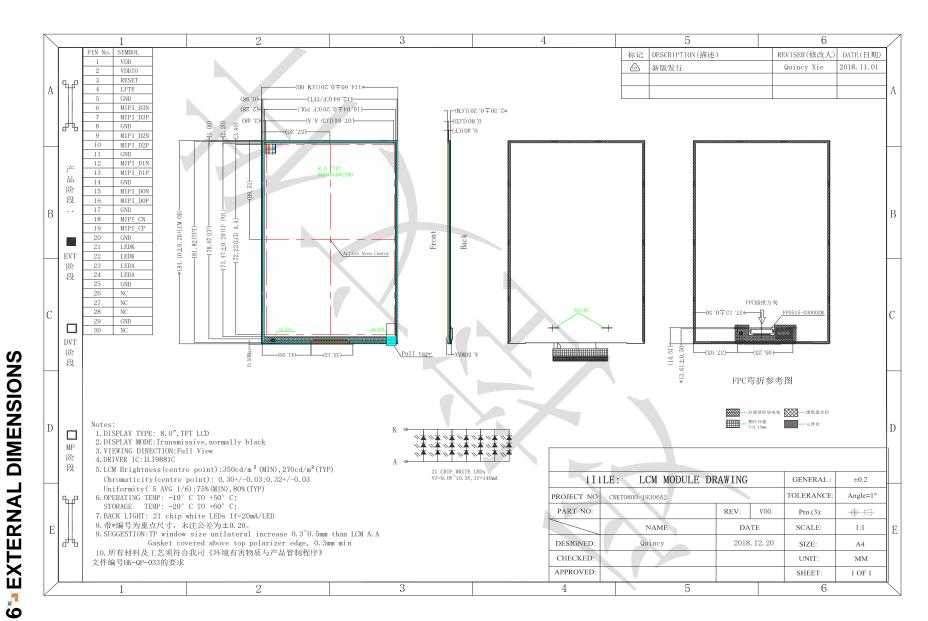

#### **4** OPERATION SPECIFTCATIONS

#### **4.1 ABSOLUTE MAXIMUM RATINGS**

| Parameter                 | Symbol Val |          | lues        | Unit             |

|---------------------------|------------|----------|-------------|------------------|

| Parameter                 | Syllibol   | Min.     | Max.        | Offic            |

| Power Voltage             | VDD        | -0.5 4.8 |             | V                |

|                           | VDDIO      | -0.5     | 3.3         | V                |

| Input Signal Voltage      | Vı         | -0.3     | VDD         | V                |

| Backlight forward current | ILED       | 0        | 21          | mA(For each LED) |

| Operating temperature     | TOP        | -10      | 50          | °C               |

| Storage temperature       | TST        | -20 60   |             | $^{\circ}$       |

| Humidity                  | RH         | -        | 90%(Max50℃) | RH               |

Note: The absolute maximum rating values of this product are not allowed to be exceeded at any times. Should a module be used with any of the absolute maximum ratings exceeded, the characteristics of the module may not be recovered, or in an extreme case, the module may be permanently destroyed.

#### **4.2 Typical Operation Conditions**

| Donomoton           | Charles         |      | 11   |     |      |

|---------------------|-----------------|------|------|-----|------|

| Parameter           | Symbol          | Min  | Тур  | Max | Unit |

| Power Voltage       | VDD             | 3.0  | 3.3  | 3.6 | V    |

|                     | VDDIO           | 1.65 | 1.8  | 1.9 | V    |

|                     | IVDD            | ,    | -    | -   | mA   |

| Current Consumption | Ivddio          | -    | -    | -   | mA   |

|                     | lвL             | -    | 140  |     | mA   |

| Dower Consumption   | PLCD            | -    | TBD  | -   | W    |

| Power Consumption   | P <sub>BL</sub> | -    | 1.37 | -   | W    |

Note :Frame Rate=60Hz,VDD=3.3V,DC Current; Operating at 25 ℃ at white pattern.

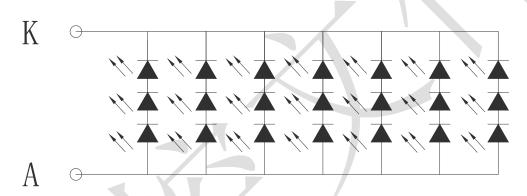

## **5** BACKLIGHT CHARACTERISTICS

| Item            | Symbol | Min | Тур                 | Max  | Unit  | Condition  |

|-----------------|--------|-----|---------------------|------|-------|------------|

| Forward voltage | Vf     | 9   | 9.75                | 10.5 | V     | If 440 = A |

| Luminance       | LV     | 220 | 270                 | -    | cd/m² | lf=140mA   |

| Number of LED   | -      |     | 21                  |      |       | -          |

| Connection mode | р      | Sei | Series and parallel |      |       | -          |

21 CHIP WHITE LEDs Vf=9.0V~10.5V, If=140mA

# 子有腮 SHENZHEN CNK ELECTRONIC CO 颐 派二二条

## 7 Interface Signal

| Pin No.    | Symbol    | Description                           |  |  |  |

|------------|-----------|---------------------------------------|--|--|--|

| 1          | VDD       | Power supply(3.3V)                    |  |  |  |

| 2          | VDDIO     | Power supply(1.8V)                    |  |  |  |

| 3          | RESET     | Reset pin(typ 1.8V)                   |  |  |  |

| 4          | LPTE      | Tearing Effect pin of each scan line. |  |  |  |

| 5          | GND       | Power ground                          |  |  |  |

| 6          | MIPI_3N   | MIPI data pair 3 negative signal      |  |  |  |

| <b>S</b> 7 | MIPI_3P   | MIPI data pair 3 positive signal      |  |  |  |

| 8          | GND       | Power ground                          |  |  |  |

| 9          | MIPI_2N   | MIPI data pair 2 negative signal      |  |  |  |

| 10         | MIPI_2P   | MIPI data pair 2 positive signal      |  |  |  |

| 11         | GND       | Power ground                          |  |  |  |

| 12         | MIPI_1N   | MIPI data pair 1 negative signal      |  |  |  |

| 13         | MIPI_1P   | MIPI data pair 1 positive signal      |  |  |  |

| 14         | GND       | Power ground                          |  |  |  |

| 15         | MIPI_ON   | MIPI data pair 0 negative signal      |  |  |  |

| 16         | MIPI_0P   | MIPI data pair 0 positive signal      |  |  |  |

| 17         | GND       | Power ground                          |  |  |  |

| 18         | MIPI_CLKN | MIPI CLK negative signal              |  |  |  |

| 19         | MIPI_CLKP | MIPI CLK positive signal              |  |  |  |

# >>> 深圳市希恩凯电子有限公司

SHENZHEN CNK ELECTRONIC CO.,LTD.

| 20 | GND  | Power ground |

|----|------|--------------|

| 21 | LEDK | LED Cathode  |

| 22 | LEDK | LED Cathode  |

| 23 | LEDA | LED Anode    |

| 24 | LEDA | LED Anode    |

| 25 | GND  | Power ground |

| 26 | NC   | Not connect  |

| 27 | NC   | Not connect  |

| 28 | NC   | Not connect  |

| 29 | GND  | Power ground |

| 30 | NC   | Not connect  |

Connector: FP0515-03000ZM Or equivalent

#### **8** SIGNAL TIMING CHARACTERISTICS

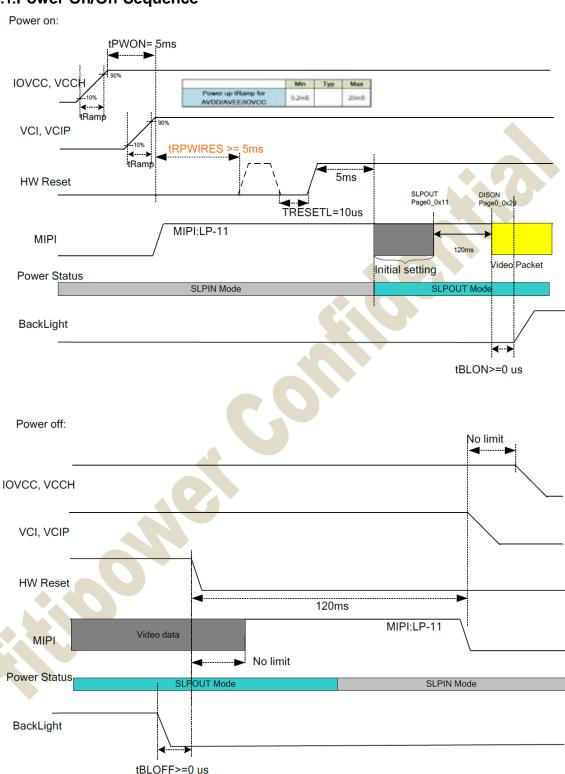

#### 8.1.Power On/Off Sequence

Note:IOVCC=VDDIO.Power supply 1.8V.

#### 8.2 MIPI Interface Timing Sequence

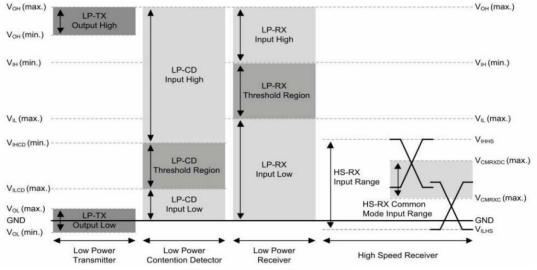

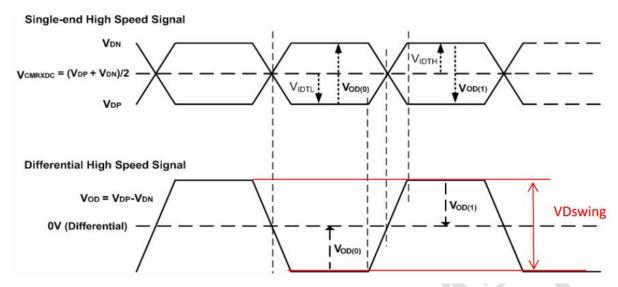

#### 1) MIPI interface DC characteristic :

|                              | Item                                                                                                    |           | Min. | Тур. | Max. | Unit |

|------------------------------|---------------------------------------------------------------------------------------------------------|-----------|------|------|------|------|

|                              | Thevenin output high level                                                                              |           | 1.1  | 1.2  | 1.3  | V    |

| LP_TW                        | Thevenin output low level                                                                               | VOL       | -50  |      | 50   | mV   |

|                              | Output impedance of LP transmitter                                                                      | ZOLP      | 110  | _    | _    | Ω    |

|                              | Common-mode voltage HS receive mode                                                                     | VCMRX(DC) | 70   | _    | 330  | mV   |

|                              | Differential input high threshold                                                                       | VIDTH     | _    | _    | 70   | mV   |

|                              | Differential input low threshold  HS_RX Single-ended input high voltage  Single-ended input low voltage |           | -70  | _    | _    | mV   |

| HS_RX                        |                                                                                                         |           | _    | _    | 460  | mV   |

|                              |                                                                                                         |           | -40  | _    | _    | mV   |

|                              | Single-ended threshold for HS termination enable                                                        |           | _    | _    | 450  | mV   |

| Differential input impedance |                                                                                                         | ZID       | 80   | 100  | 125  | Ω    |

|                              | Logic 1 input voltage                                                                                   | VIH       | 880  | _    | 1350 | mV   |

| LP_RX                        | Logic 0 input voltage. not in ULPState                                                                  | VIL       | 0    | _    | 550  | mV   |

|                              | Input hysteresis                                                                                        | VHYST     | 25   | _    | _    | mV   |

| LP_CD                        | Logic 1 contention threshold                                                                            | VIHCD     | 450  | _    | 1350 | mV   |

| LF_CD                        | Logic 1 contention threshold                                                                            | VILCD     | 0    | _    | 200  | mV   |

Figure 1. MIPI DC Diagram

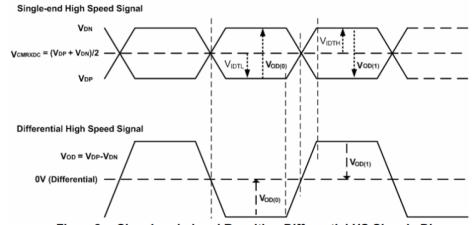

Figure 2. Signal-ended and Resulting Differential HS Signals Diagram

# 深圳市希恩凯电子有限公司 K SHENZHEN CNK ELECTRONIC CO.,LTD.

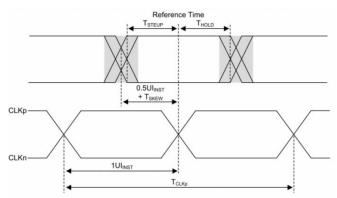

2) MIPI data to clock timing definitions

| Clock Parameter                                    | Symbol         | Min   | Тур. | Max. | Unit    |

|----------------------------------------------------|----------------|-------|------|------|---------|

| UI instantaneous                                   | UI INST        | 2     | _    | 12.5 | ns      |

| Data to Clock Setup<br>Time[Receiver]              | T<br>SETUP[RX] | 0.15  | _    | _    | UI INST |

| Clock to Data Hold<br>Time[Receiver]               | T<br>HOLD[RX]  | 0.15  | _    | _    | UI INST |

| Data to Clock Skew<br>(Measured at<br>transmitter) | T<br>SKEW[TX]  | -0.15 | _    | 0.15 | _       |

#### [Note]

- \*1) This max value corresponds to a minimum 80 Mbps data rate per lane

- \*2) The minimum UI shall not be violated for any single bit period, i.e., any DDR half cyclewithin a data burst.

- \*3) Total silicon and package delay budget of 0.3 UIINST

- \*4) Total setup and hold window for receiver of 0.3\* UIINST

- \*5) T SETUP[Rx] and T HOLD[RX] are only for RX without FPCB and connector and guaranteed by design.

Figure3. MIPI data to clock timing definitions

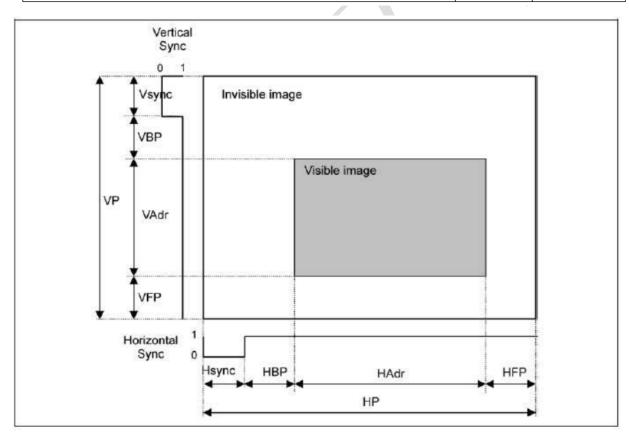

# 深圳市希恩凯电子有限公司 SHENZHEN CNK ELECTRONIC CO.,LTD. 8.3 Timing Chart

|                            | ITEM SYNBOL |                               |        |         | UNIT             |

|----------------------------|-------------|-------------------------------|--------|---------|------------------|

| LCD                        |             | Frame Rate -                  |        | (60)    | Hz               |

|                            | DCLK        | Frequency                     | fCLK   | (68.43) | MHz              |

|                            | DCLK        | Period                        | Tclk   | (14.61) | ns               |

|                            |             | Horizontal total time         | tHP    | (880)   | t <sub>CLK</sub> |

|                            |             | Horizontal Active time        | tHadr  | (800)   | t <sub>CLK</sub> |

|                            | Horizontal  | Horizontal Pulse Width        | tHsync | (5)     | t <sub>CLK</sub> |

|                            |             | Horizontal Back Porch         | tHBP   | (59)    | t <sub>CLK</sub> |

| Timing                     |             | <b>Horizontal Front Porch</b> | tHFP   | (16)    | t <sub>CLK</sub> |

|                            |             | Vertical total time           | tvp    | (1296)  | t <sub>H</sub>   |

|                            |             | Vertical Active time          | tVadr  | (1280)  | t <sub>H</sub>   |

|                            | Vertical    | Vertical Pulse Width          | tVsync | (5)     | t <sub>H</sub>   |

|                            |             | Vertical Back Porch           | tVBP   | (3)     | t <sub>H</sub>   |

|                            |             | Vertical Front Porch          | tVFP   | (8)     | t <sub>H</sub>   |

| Differential Swing VDswing |             | VDswing                       | (250)  | mV      |                  |

| Bit Rate TX SPD(M          |             | TX SPD(MBPS)                  | (450)  | Mbps    |                  |

|                            | Pixel Fomat |                               |        | (888)   | Data bit/pixel   |

|                            | Lane        |                               |        | 4       | Lane             |

# 深圳市希恩凯电子有限公司 K SHENZHEN CNK ELECTRONIC CO.,LTD.

# 深圳市希恩凯电子有限公司 SHENZHEN CNK ELECTRONIC CO.,LTD.

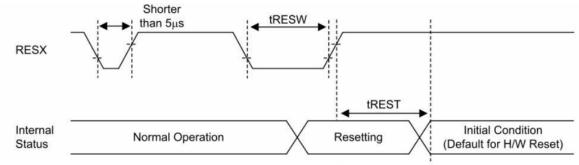

#### 8.4 Reset Input Timing

| Symbol | Parameter             | Pad  | Min. | Typ. | Max.   | Unit | Note                        |  |

|--------|-----------------------|------|------|------|--------|------|-----------------------------|--|

| tRESW  | Reset low pulse width | RESX | 10   |      |        | us   |                             |  |

| tREST  | Reset completion time | RESX |      |      | 5      |      | Reset during Sleep In mode  |  |

|        |                       | RESX |      |      | 120(5) | ms   | Reset during Sleep Out mode |  |

Figure4. Reset Input Timing

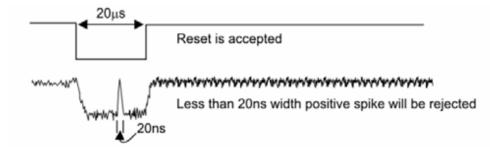

#### Note]

\*1) Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below.

| RESX Pulse           | Action         |  |  |

|----------------------|----------------|--|--|

| Shorter than 5us     | Reset Rejected |  |  |

| Longer than 10us     | Reset          |  |  |

| Between 5us and 10us | Reset Start    |  |  |

- \*2) During the reset period, the display will be blanked. (The display is entering blanking sequence, for which the maximum time is 120ms, when Reset starts is sleep out-mode. The display remains in the blank state is Sleep In-mode) and then return to default condition for H/W reset.

- \*3) During Reset Completion Time, ID bytes (or similar) value in MTP block will be latched to the the rnal register during this period. This loading is done every time when there is H/W reset complete

time (tREST) within 5ms after a rising edge of RESX.

\*4) Spike Rejection also applies during a valid reset pulse as shown below:

\*5) It is necessary to wait for 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

## 9 ELECTRO-OPTICAL CHARACTERISTICS

| Item                     |                   | Symbol     | Condition             | Min  | Тур  | Max  | Unit  | Remark           |

|--------------------------|-------------------|------------|-----------------------|------|------|------|-------|------------------|

| Response time            |                   | Tr+Tf      |                       | -    | 25   | 30   | ms    | Note 2<br>Note 3 |

| Contrast ratio           |                   | Cr         | θ=0° □<br>Ta=25 °C    | 600  | 800  | -    | -     | Note 2<br>Note 4 |

| Luminance<br>uniformity  |                   | δ<br>WHITE |                       | 75   | 80   |      | %     | Note 2<br>Note 6 |

| Surface Lumina           | Surface Luminance |            |                       | 220  | 270  | -    | cd/m² | Note 2           |

| Viewing angle range      |                   |            | □ =90°                | -    | 85   | -    | deg   | Note1            |

|                          |                   | θ          | □ =270° □ =0° □ =180° | -    | 85   | - /  | deg   |                  |

|                          |                   | ŭ          |                       | -    | 85   | -    | deg   |                  |

|                          |                   |            |                       | -    | 85   | -    | deg   |                  |

|                          | Red               | х          |                       | -    | -    | -    |       | Note 2<br>Note 5 |

|                          | Neu               | у          | θ=0°<br>Ta=25 ℃       | -    | 1    | -    |       |                  |

|                          | Green             | x          |                       | -    | -    | -    |       |                  |

| CIE(x,y)<br>chromaticity | Gleen             | у          |                       | -    | -    | -    |       |                  |

|                          | Blue              | x          |                       | 7    | -    | -    |       |                  |

|                          |                   | у          |                       | -    | -    | -    |       |                  |

|                          | White             | x          |                       | 0.27 | 0.30 | 0.33 |       |                  |

|                          | vviiite           | у          |                       | 0.29 | 0.32 | 0.35 |       |                  |

# 深圳市希恩凯电子有限公司 K SHENZHEN CNK ELECTRONIC CO.,LTD.

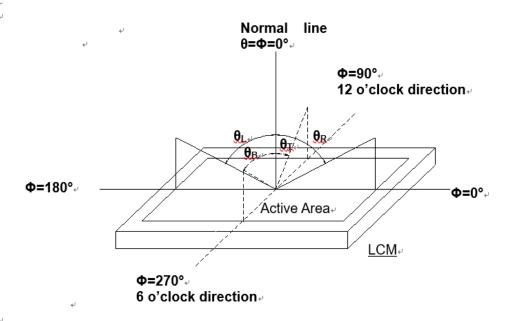

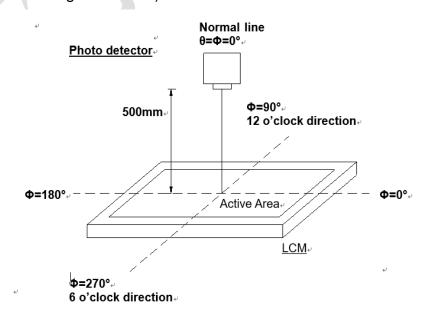

Note 1: Definition of viewing angle range

Viewing angle is the angle at which the contrast ratio is greater than 10. The viewing angles are determined for the horizontal or 3, 9 o'clock direction and the vertical or 6, 12 o'clock direction with respect to the optical axis which is normal to the LCD surface

#### Definition of viewing angle-

Note 2: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 30 minutes operation, the optical properties are measured at the center point of the LCD screen. (Viewing angle is measured by ELDIM-EZ

contrast/Height :1.2mm ,Response time is measured by Photo detector TOPCON BM-7, other items are measured by BM-5A/

Field of view: 1° /Height: 500mm.)

# 深圳市希恩凯电子有限公司 SHENZHEN CNK ELECTRONIC CO.,LTD.

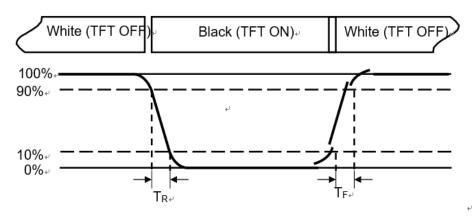

Note 3: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time ( $T_R$ ) is the time between photo detector output intensity changed from 90% to 10%. And fall time ( $T_F$ ) is the time between photo detector output intensity changed from 10% to 90%.

Definition of response time-

Note 4: Definition of contrast ratio

Contrast ratio (CR) =  $\frac{\text{Luminance measured when LCDon the "White" state}}{\text{Luminance measured when LCDon the "Black" state}}$

Note 5: Definition of color chromaticity (CIE1931)

Color coordinates measured at center point of LCD.

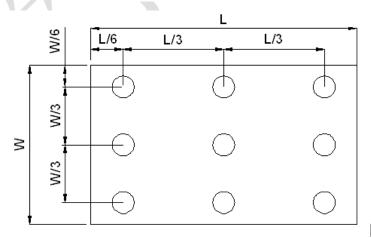

Note 6: Definition of Luminance Uniformity ("White" state)

Active area is divided into 9 measuring areas. Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (Yu) =

$$\frac{B_{min}}{B_{max}}$$

Definition of measuring points-

B<sub>max</sub>: The measured maximum luminance of all measurement position.

B<sub>min</sub>: The measured minimum luminance of all measurement position.

#### **10™RELIABILITY TEST**

#### Reliability test conditions ( Polarizer characteristics null )

| No. | Test Items                             | Test Condition                                                | Remarks                    |  |

|-----|----------------------------------------|---------------------------------------------------------------|----------------------------|--|

| 1   | High Temperature Storage               | T = 60°C for 96hr                                             |                            |  |

| 2   | Low Temperature Storage                | T = -20°C for 96hr                                            | Module                     |  |

| 3   | High Temperature Operating             | T = 50°C for 96hr                                             |                            |  |

| 4   | Low Temperature Operating              | T = -10°C for 96hr<br>(But no condensation of dew)            | (Without<br>Contamination) |  |

| 5   | High Temp. and High Humidity Operating | T = 50°C /90% for 96hr<br>(But no condensation dew)           | X                          |  |

| 6   | Thermal Shock                          | -10±2°C~25~50±2°C×10cycles<br>(30min.) (5min.) (30min.)       |                            |  |

| 7   | Packing Shock                          | 1corner, 3edge, 6face / 76cmDrop                              |                            |  |

| 8   | Packing Vibration                      | Random 1.06Grms XYZ 30min for each direction                  | Packing                    |  |

| 9   | Electrostatic Discharge                | Contact: ±4KV<br>Air: ±8KV<br>150PF/330Ω,5Points/panel,5times | Class B.Note1              |  |

- ※ 1) No.1~ No.6: No guarantee for panel, only for module with the above test conditions.

- ※2) No.7~ No.8: Refer to 7-1) Packing Ass'y on page 14.

#### Note1

| Class | Performance                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| A     | All functions perform as designed during and after exposure to interference             |

| В     | Temporary degradation or less of performance which is self-recoverable                  |

| С     | Degradation or less of performance which requires operator intervention or system reset |

| C     | to recover                                                                              |

| D     | Degradation or less of function which is not recoverable                                |

#### Result Evaluation Criteria

TFT- LCD Panel should be at room temperature for 2 hours when the display quality test is over. There should be no particular change which might affect the practical display function and the display quality test should be conducted under normal operating condition.

TBD

## 12 Package Drawing

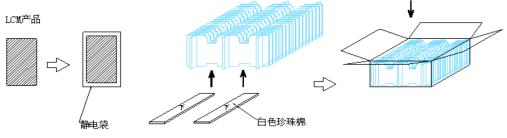

#### LCM 产品(刀卡类)包装流程图

LCM Product(Card Type) Packing Flow Diagram

#### 1.0 包装材料清单请参考 LCM BOM;

Packing BOM: Please Reference the LCM BOM

#### 2.0 包装方法 (Packing Procedure)

#### 第一步

将产品装入静电袋

#### First step

Putting every piece of LCM into anti-static bag.

#### 第二步

把长卡、短卡组成卡阵(短卡朝向一致) 形状和数量按照 BOM 实际物料,卡阵底 部放对应的白色珍珠棉后装箱

#### Second step

Assemble a carton matrix with the right white EPE down below ,then place them into the carton.

#### 第三步

每个卡槽内放两片产品, 2片产品显示面相对, 中间粉色珍珠棉一起

#### Third step

Put a pink EPE between 2 pcs products(face to face) while insert all of them into the carton matrix.

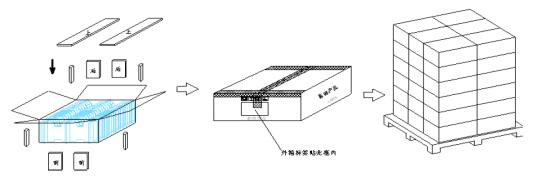

#### 第四步

装箱后,按照 BOM 实际物料在 纸箱内侧与卡阵避空位置放白色 泡棉;

#### Fourth step

Insert all other white EPE into the right place of the carton matrix.

#### 第五步

用胶带封箱,贴外箱标签

#### Fifth step

seal the carton with cellulose tape;

Stick on a carton label,

#### 第六步

将箱子整齐的放在栈板 上并包裹,最高可堆叠 6层;

#### Sixth step

Place the boxes together on a pallet (6 layers at most),